5. NMI Handling in Nuclei processor core

5.1. NMI Overview

NMI (Non-Maskable Interrupt) is a special input signal of the processor core, often used to indicate system-level emergency errors (such as external hardware failures, etc.). After encountering the NMI, the processor should abort execution of the current program immediately and process the NMI error instead.

5.2. NMI Masking

In the RISC-V architecture, NMI cannot be masked, which means if the core encounters an NMI, it must stop current execution and turns to handle the NMI.

5.3. Entering NMI Handling Mode

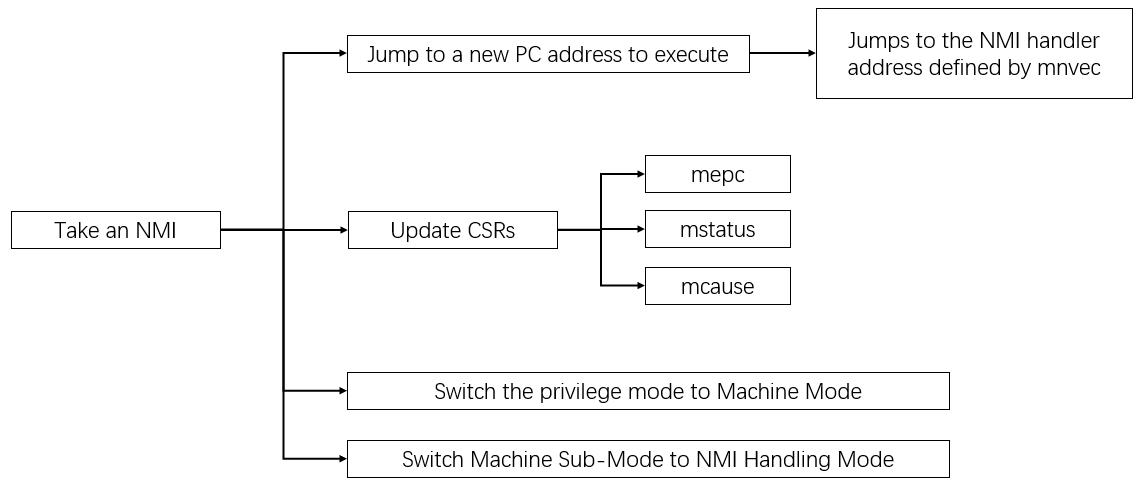

Taking an NMI, hardware behaviors of the Nuclei processor core are described as shown in The overall process of NMI. Note that the following operations are done simultaneously in one cycle:

Update the CSR registers: mepc and mstatus.

These behaviors are following RISC-V standard privileged architecture specification. This document will not repeat its content, please refer to RISC-V standard privileged architecture specification for more details.

Update the CSR registers: mcause.

The value of mcause for NMI is unique in Nuclei processor core, and will be detailed in the following section.

Stop the execution of the current program, and start from the PC address defined by the CSR mnvec.

The value of mnvec is unique in Nuclei processor core, and will be detailed in the following section.

Update the Privilege Mode and Machine Sub-Mode of the core.

This is unique in Nuclei processor core, and will be detailed in the following section.

Fig. 5.1 The overall process of NMI

5.3.1. Execute from the PC Defined by mnvec

The Nuclei processor core jumps to the PC defined by the CSR mnvec after encountering an NMI. The CSR mnvec has two potential values controlled by CSR register mmisc_ctl:

When mmisc_ctl[9]=1, the value of mnvec is equal to the value of mtvec, which means NMIs and exceptions share the same trap entry address.

When mmisc_ctl[9]=0, the value of mnvec equals to the value of reset_vector which is the PC value after a reset. The reset_vector is the core’s input signal. Please refer to the specific datasheet of the Nuclei processor core for details about this signal.

5.3.2. Update the CSR mcause

The Nuclei processor core will save the NMI code into the CSR mcause.EXCCODE by the hardware automatically when take a NMI. Interrupts, exceptions and NMIs all have their own specified Trap ID. The Trap ID of NMI has two potential values controlled by CSR register mmisc_ctl:

When mmisc_ctl[9]=1, the Trap ID of NMI is 0xfff.

When mmisc_ctl[9]=0, the Trap ID of NMI is 0x1.

The software can recognize the Trap reason querying the Trap ID, and build the corresponding trap handler program for different types of traps.

5.3.3. Update the Privilege Mode

NMI is handed in Machine Mode, so the privilege mode will be switched to Machine Mode when the core takes an NMI.

5.3.4. Update the Machine Sub-Mode

The Machine Sub-Mode of the Nuclei processor core is indicated in the msubm.TYP filed in real time. When the core takes an NMI, the Machine Sub-Mode will be updated to NMI handling mode, so:

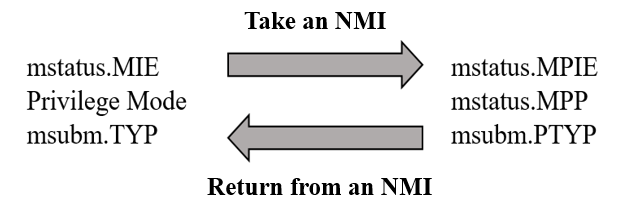

The filed msubm.TYP is updated to NMI handling mode, as described in The CSR mstatus and msubm updating when enter/exit the NMI, to reflect the current Machine Sub-Mode is “NMI handling mode”.

The value of msubm.PTYP will be updated to the value of msub.TYP before taking the NMI, as shown in The CSR mstatus and msubm updating when enter/exit the NMI. The value of msubm.PTYP will be used to restore the value of msubm.PTYP after exiting the NMI handler.

Fig. 5.2 The CSR mstatus and msubm updating when enter/exit the NMI

5.4. Exit the NMI Handling Mode

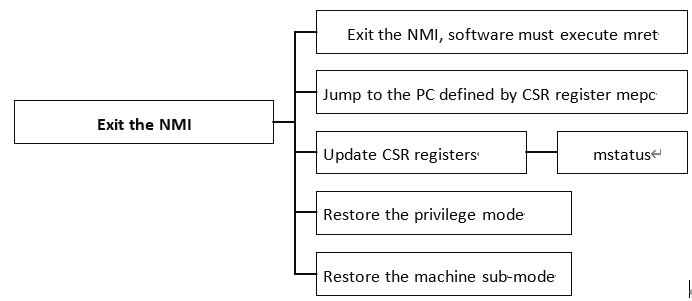

After handling the NMI, the core needs to exit from the NMI handler eventually, and return to execute the main program. Since the NMI is handling in Machine Mode, the software has to execute mret to exit the NMI handler.

The hardware behavior of the processor after executing mret instruction is as shown in The overall process of exiting an NMI. Note that the following hardware behaviors are done simultaneously in one cycle:

Stop the execution of the current program, and start from the PC address defined by the CSR mepc. Update the CSR mstatus.Update the Privilege Mode.

These behaviors are following RISC-V standard privileged architecture specification. And the behaviors are exactly same as the behaviors Exit the Exception Handling Mode, this document will not repeat its content here, please refer to RISC-V standard privileged architecture specification for more details.

Update the Machine Sub-Mode.

This is unique in Nuclei processor core, and will be detailed in the following section.

Fig. 5.3 The overall process of exiting an NMI

5.4.1. Update the Machine Sub-Mode

The value of msubm.TYP indicates the Machine Sub-Mode of the Nuclei processor core in real time. After executing the mret instruction, the hardware will automatically restore the core’s Machine Sub-Mode by the value of msubm.PTYP:

Taking an NMI, the value of msubm.PTYP is updated to the Machine Sub-Mode before taking the NMI. After executing the mret instruction, the hardware will automatically restore the Machine Sub-Mode using the value of msubm.PTYP, as shown in The CSR mstatus and msubm updating when enter/exit the NMI. Through this mechanism, the Machine Sub-Mode of the core is restored to the same mode before taking the NMI.

5.5. NMI Service Routine

When the core takes an NMI, it will jump to execute the program at the address defined by mnvec, which is usually the NMI service routine.

Note: Since there is no hardware to save and restore the execution context automatically when take or exit an NMI, so the software needs to explicitly use the instruction (in assembly language) for context saving and restoring.

5.6. NMI Nesting

Please see Nesting of Interrupt, NMI and Exception for more details.